Innovation for the next generation

# AT4039B-JIT

4-Lane BERT | 28 Gbps NRZ

4 Differential Error Detectors with CDR | 4 Differential Pulse Pattern Generators | Adaptive FFE on receivers | Receiver Sensitivity | Jitter and Interference Injection | ISI Channel Emulator

# Summary

The AT line of products is highly integrated for the Advantest V93000 system and fits right underneath the load board, in the cavity of the test head extender. Due to this, the signal path to the DUT is kept extremely short.

The AT line of instruments is made to work for packaged silicon systems as well as for wafer probing and is meant to enable at-speed testing of SerDes, transceivers, amplifiers and other active and passive high-speed digital components. The AT family consists of pattern generators, error detectors and sampling oscilloscopes.

# AT4039B-JIT

## **100G BERT**

### Introduction

The AT4039B-JIT is a full feature four-lane differential 100 Gb/s NRZ BERT that covers bitrates of 1.25 to 28.125 Gbps. AT4039B-JIT enables jitter tolerance testing with sinusoidal jitter injection up to 100 MHz.

The GUI makes it possible to individually control each TX level. The user may also inject error sequences into the stream. The receiver features a combination of DFE and FFE equalization that compensates for up to 30 dB of loss at Nyquist and a CTLE equalizer with 10 dB dynamic range.

# **Key Features**

#### **Transmit**

- Low cost, instrument-grade BERT optimized for high speed data analysis and JTOL of 100G transceivers.

- The wide range of bitrate coverage allows physical testing for Ethernet, HDMI 2, USB 3.1, PCle, Fiber-Channel and others.

- Ability to tune the bit rate in very fine steps to facilitate finding the locking margin.

- Supports user-defined patterns.

Figure 1: Sinusoidal and Random Jitter Injection

#### Receive

- Adaptive equalizer and channel IL estimator > 10 dB (FFE+DFE).

- Control of CTLE slider channel by channel

- Quadruple port CDR, being able to recover the supported rates.

## **Target Applications**

- Production testing of transceivers and consumer electronics interfaces

- Testing for functional and SI functionality

- Jitter tolerance of receivers

- Transceiver functional tester, for simple validation

#### General:

- API libraries with documentation for Smartest and windows.

- LabView driver and Python wrapper available

Figure 2: SNR capture over time

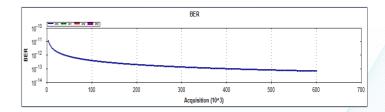

Figure 3: BER curves for one channel with 1 error inserted at the MSB and LSB respectively

# **Electrical Specifications**

| Parameter                     | Specifications                                |

|-------------------------------|-----------------------------------------------|

| Bit Rates                     | NRZ: 1.12 – 1.56 and 3.25 – 28.125 Gbps       |

| TX Amplitude Differential     | 0 – 2200 mVpp at 26 GBd                       |

| Patterns                      | PRBS 7/9/11/13/15/16/23/31 /58 - Square wave  |

| TX Amplitude Adjustment       | Steps of 2 mV                                 |

| Equalizing Filter Spacing     | 1 UI                                          |

| Random Jitter RMS             | 320 fs                                        |

| Rise / Fall Time (20–80%)     | 14 / 14 ps                                    |

| Error Detector sensitivity    | 30 mVpp                                       |

| SJ Amplitude max              | 100 ps                                        |

| SJ Frequency                  | 40 kHz to 100 MHz                             |

| Inter-Lane Skew               | Supported up to 100 ps                        |

| Error Detector CDR            | Supported                                     |

| Input Equalizer Dynamic Range | Up to 30 dB                                   |

| TX/RX connectors              | Blind-mate SMPM                               |

| Reference clock Output        | Bitrate / 32, 64, 165 LVPECL                  |

| Clock Input Range             | 80-700 MHz with an optimal value of 156.25MHz |

| Clock Input Amplitude         | 200 - 1200 mV                                 |

| Clock Input Impedance         | 50 Ω                                          |

| Temperature range             | -15 to 75 °C                                  |

| Weight                        | ~1.5 kg                                       |

| Power (ATE version only)      | 12 V, 1.5A                                    |

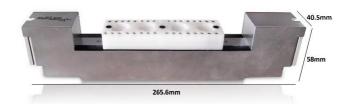

### **Mechanical Dimensions**

The AT4039B-JIT is customized to fit and seamlessly function inside an Advantest HSIO test head extender.

Dimensions: 265.6 x 40.5 x 58 mm3

# **Ordering Information**

| Option      | Description             |

|-------------|-------------------------|

| AT4039B-JIT | 4 Channels 28 Gbps BERT |

Please contact us at <a href="mailto:sales@multilaneinc.com">sales@multilaneinc.com</a>.

#### **North America**

48511 Warm Springs Blvd. Suite 310 Fremont, CA 94539 USA +1 510 573 6388

#### Worldwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 5 941 668

#### Asia

14F-5/ Rm.5, 14F., No 295 Sec.2, Guangfu Rd. East Dist., Hsinchu City 300, Taiwan (R.O.C) +886 3 5744 591